-

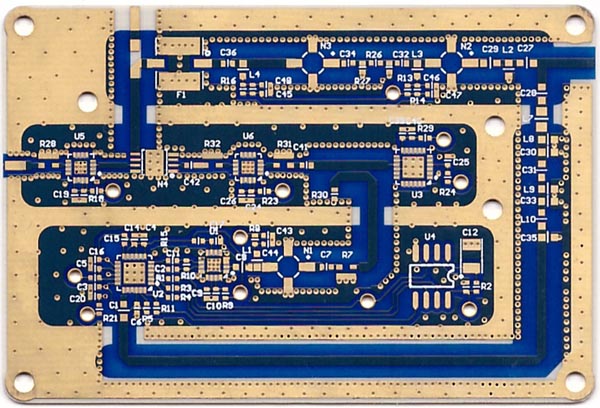

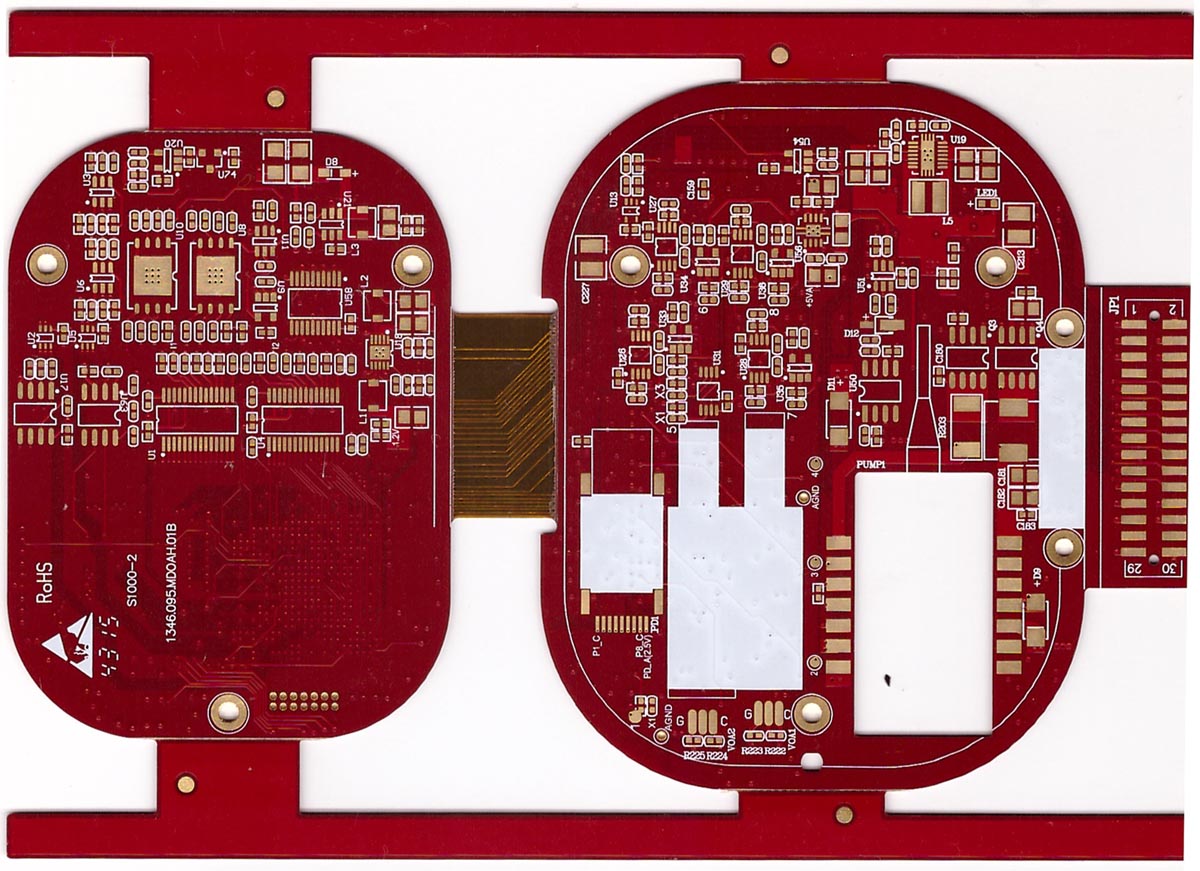

抗干扰设计的基本任务是系统或设备不会由于外部电磁干扰的影响而发生故障或功能丧失,也不会对外界发出过多的噪声干扰,以免影响正常运行其他系统或设备。因此提高系统的抗干扰能力也是系统设计的重要组成部分。电路抗干扰设计原理总结:1,电源线的设计(1)选择合适的电源;(2)尽量扩大电源线;(3)确保电力线,底线和数据传输方向一致;(4)使用抗干扰元件;(5)在电源插座上加入去耦电容(10〜100uf)。2,地面的设计(1)独立的模拟和数字地;(2)尽可能使用单点接地;(3)尽可能扩大地面;(4)将敏感电路连接到稳定的接地参考源;(5)用于将高带宽噪声电路与低频电路分开的pcb板分区设计;(6)最小化接地回路的面积(所有设备在电源被称为“接地回路”后返回地面形成的路径)。3,组件的配置(1)没有长的平行信号线;(2)确保PCB的时钟发生器,晶体振荡器和CPU的时钟输入尽可能靠近并远离其他低频元件;(3)应在核心器件周围配置器件,以尽量减少引线长度;(4)PCB板的分区布局;(5)考虑机箱中的PCB板位置和方向;(6)缩短高频元件之间的导线。4,去耦电容配置(1)每10个集成电路添加一个充放电电容器(10uf);(2)引线型电容器用于低频,片状电容器用于高频;(3)每个集成芯片上应放置一个0.1uf陶瓷电容;(4)抗击噪声的能力较弱,在关机期间电源变化较大的设备应增加高频去耦电容。(5)不要在电容器之间共用过孔;(6)去耦电容器引线不能太长。5,降低噪音和电磁干扰原理(1)使用45°多段线而不是90°多段线(尽量减少高频信号对外界的发射和耦合);(2)使用串联电阻来降低电路信号边沿的转换速率;(3)石英晶体壳应接地;(4)不要将未使用的电路悬空;(5)时钟垂直于IO线时干扰小;(6)尽量将电动势保持在零点附近;(7)IO驱动电路尽可能靠近PCB的边缘;(8)不要在任何信号上形成回路;(9)对于高频板,电容的分布电感不能忽略,电感的分布电容不容忽视;(10)电源线和交流线通常应与信号线位于不同的电路板上。6,其他设计原则(1)CMOS未使用的引脚应接地或通过电阻供电;(2)RC电路用于吸收继电器和其他原件的放电电流;(3)在总线上增加约10k个上拉电阻有助于防止干扰;(4)全解码抗干扰性能更好;(5)元件不必通过10k电阻连接到电源;(6)巴士应尽可能短以保持相同的长度;(7)两层之间的布线应尽可能垂直;(8)发热元件避免敏感元件;(9)只要空间允许,正面水平排列,负垂直排列,越厚越好(只有地面和电源线);(10)要有良好的分层线,最好从前面跑,反之亦然;(11)保持足够的距离,如滤波器输入和输出,光电耦合器输入和输出,交流电源线和弱信号线;(12)长线加低通滤波器。曲线应尽可能短,必须将长线插入合理位置的C,RC或LC低通滤波器;(13)除地面线外不要使用粗线。7,接线宽度和电流(1)总宽度不应小于0.2mm(8mil);(2)在高密度和高精度PCB上,节距和线宽一般为0.3mm(12mil);(3)当铜箔厚度约为50um时,导线宽度为1〜1.5mm(60mil)= 2A;(4)公共用地一般为八亿立方米。应该注意微处理器的应用。8,电源线电源线应尽可能短并采取直线。最好走在树上,不要绕着一圈走。9,布局首先,考虑PCB